March 1997

### Features

- Single Chip UART/BRG

- DC to 625K Baud (DC to 10MHz Clock)

- Crystal or External Clock Input

- On Chip Baud Rate Generator 1 to 65535 Divisor Generates 16X Clock

- Prioritized Interrupt Mode

- Fully TTL/CMOS Compatible

- Microprocessor Bus Oriented Interface

- 80C86/80C88 Compatible

- Scaled SAJI IV CMOS Process

- Low Power 1mA/MHz Typical

- Modem Interface

- Line Break Generation and Detection

- Loopback and Echo Modes

- Doubled Buffered Transmitter and Receiver

- Single 5V Supply

## Ordering Information

| PACKAGE | TEMPERATURE<br>RANGE ( <sup>O</sup> C) | 625K BAUD    | PKG.<br>NO. |

|---------|----------------------------------------|--------------|-------------|

| PDIP    | 0 to +70                               | CP82C50A-5   | E40.6       |

|         | -40 to +85                             | IP82C50A-5   | E40.6       |

| PLCC    | 0 to +70                               | CS82C50A-5   | N44.65      |

|         | -40 to +85                             | IS82C50A-5   | N44.65      |

| CERDIP  | 0 to +70                               | CD82C50A-5   | F40.6       |

|         | -40 to +85                             | ID82C50A-5   | F40.6       |

|         | -55 to +125                            | MD82C50A-5/B | F40.6       |

# **Functional Diagram**

# Description

The 82C50A Asynchronous Communication Element (ACE) is a high performance programmable Universal Asynchronous Receiver/Transmitter (UART) and Baud Rate Generator (BRG) on a single chip. Using Harris Semiconductor's advanced Scaled SAJI IV CMOS Process, the ACE will support data rates from DC to 625K baud (0-10MHz clock).

82C50A

**CMOS** Asynchronous

**Communications Element**

The ACE's receiver circuitry converts start, data, stop, and parity bits into a parallel data word. The transmitter circuitry converts a parallel data word into serial form and appends the start, parity, and stop bits. The word length is programmable to 5, 6, 7, or 8 data bits. Stop bit selection provides a choice of 1,1.5, or 2 stop bits.

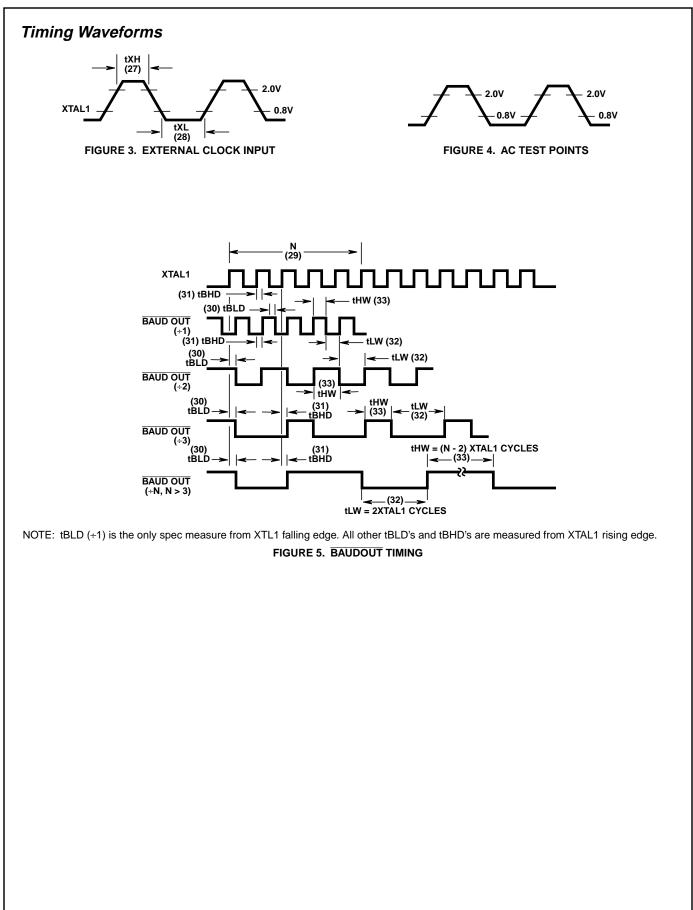

The Baud Rate Generator divides the clock by a divisor programmable from 1 to 2<sup>16</sup>-1 to provide standard RS-232C baud rates when using any one of three industry standard baud rate crystals (1.8432MHz, 2.4576MHz, or 3.072MHz). A programmable buffered clock output (BAUDOUT) provides either a buffered oscillator or 16X (16 times the data rate) baud rate clock for general purpose system use.

To meet the system requirements of a CPU interfacing to an asynchronous channel, the modem control signals  $\overline{\text{RTS}}$ ,  $\overline{\text{CTS}}$ ,  $\overline{\text{DSR}}$ ,  $\overline{\text{DTR}}$ ,  $\overline{\text{RI}}$ ,  $\overline{\text{DCD}}$  are provided. Inputs and outputs have been designed with full TTL/CMOS compatibility in order to facilitate mixed TTL/NMOS/CMOS system design.

| Unai | Diagi    | am            |              |                      |                            |               |                   |        |  |

|------|----------|---------------|--------------|----------------------|----------------------------|---------------|-------------------|--------|--|

|      |          |               | MICROPROCESS | OR INTERFACE         |                            |               |                   |        |  |

| -    | CSO      | 12            |              |                      | 24 CSOUT                   |               |                   |        |  |

| -    | CS1      | 13            |              |                      | 23 DDIS                    |               |                   |        |  |

| -    | CS2      | 14            |              |                      |                            |               |                   |        |  |

| _    | ADS      | 25            |              | INTERRUPT<br>ENABLE, | 30 INTRPT                  |               |                   |        |  |

|      | A0       | 28            |              | ID, & CONTROL        | F                          |               |                   |        |  |

| _    | A1       | 27            |              |                      | U.                         | ART           |                   |        |  |

| -    | A2       | 26            |              |                      |                            |               | <mark>∢</mark> 10 | SIN    |  |

| -    | MR       | 35            |              |                      |                            | RECEIVER      | <b>4</b> 9        | RCLK   |  |

| _    | DISTR    | 22            |              |                      |                            | DIVISOR LATCH | 15 B              | AUDOUT |  |

| -    | DISTR    | 21            |              |                      | LINE STATUS<br>AND CONTROL | AND BAUD RATE | <b>_</b> 16       | XTAL1  |  |

|      | DOSTR    | 19            |              |                      |                            | GENERATOR     | 17                | XTAL2  |  |

| -    | DOSTR    | 18            |              |                      |                            | TRANSMITTER   | 11                | SOUT   |  |

| -    | 50       |               |              |                      |                            | INANOMITTER   | 32                | RTS    |  |

| •    | D0<br>D1 | $\frac{1}{2}$ |              |                      | МС                         | DDEM          | 33                | DTR    |  |

| •    | D2       | 3             |              |                      |                            |               | 34                | OUTI   |  |

| •    | D3       | 4             |              |                      | MODEM                      | CONTROL       | 31                | OUT2   |  |

|      | D4       | 5             |              |                      |                            |               | _36               | CTS    |  |

|      | D5       | 6             |              |                      |                            |               | 37                | DSR    |  |

|      | D6       | 7             |              |                      | MODE                       | A STATUS      | 38                | DCD    |  |

|      | D7       | 8             |              |                      |                            |               | 39                | RI     |  |

|      |          |               |              |                      |                            |               |                   |        |  |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright © Harris Corporation 1997

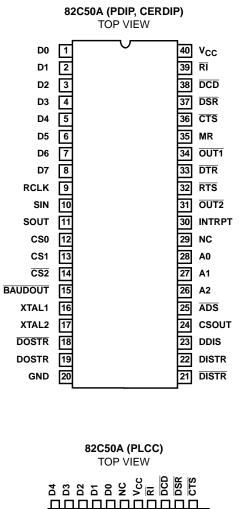

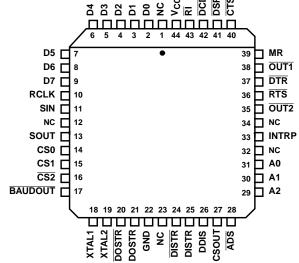

# Pin Description

| SYMBOL          | PIN<br>NUMBER | TYPE   | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------|---------------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

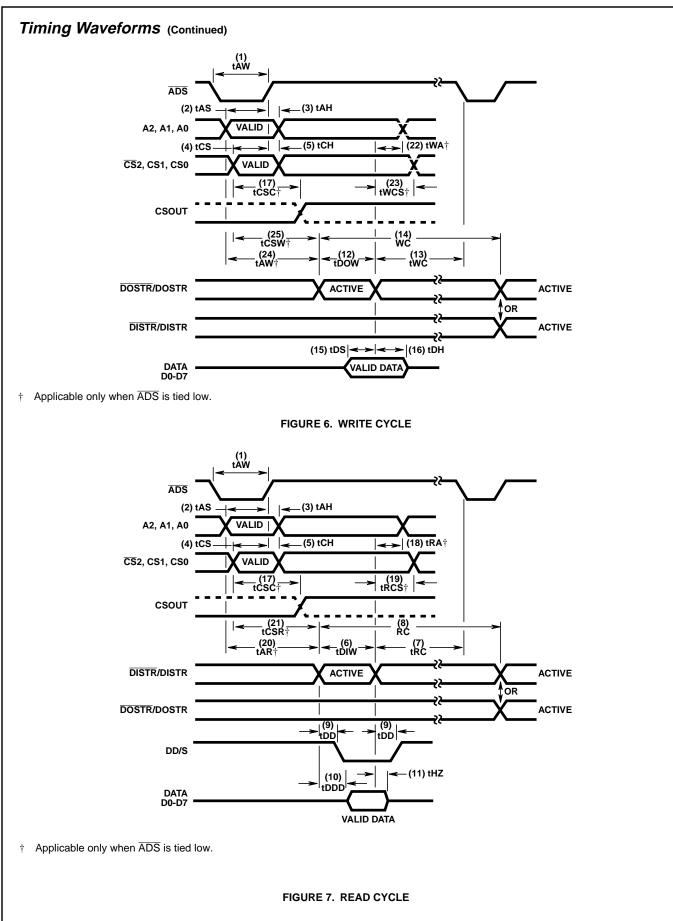

| DISTR,<br>DISTR | 22<br>21      | I      | HL              | DATA IN STROBE, DATA IN STROBE: DISTR, DISTR are read inputs which cause<br>the 82C50A to output data to the data bus (D0-D7). The data output depends upon<br>the register selected by the address inputs A0, A1, A2. The chip select inputs CS0,<br>CS1, CS2 enable the DISTR, DISTR inputs.<br>Only an active DISTR or DISTR, not both, is used to receive data from the 82C50A<br>during a read operation. If DISTR is used as the read input, DISTR should be tied<br>high. If DISTR is used as the active read input, DISTR should be tied low.                                                                                                                       |  |

| DOSTR,<br>DOSTR | 19<br>18      | <br>   | HL              | DATA OUT STROBE, DATA OUT STROBE: DOSTR, DOSTR are write inputs which cause data from the data bus (D0-D7) to be input to the 82C50A. The data input depends upon the register selected by the address inputs A0, A1, A2. The chip select inputs CS0, CS1, CS2 enable the DOSTR, DOSTR inputs.<br>Only an active DOSTR or DOSTR, not both, is used to transmit data to the 82C50A during a write operation. If DOSTR is used as the write input, DOSTR should be tied high. If DOSTR is used as the write input, DOSTR should be tied low.                                                                                                                                  |  |

| D0-D7           | 1-8           | I/O    |                 | DATA BITS 0-7: The Data Bus provides eight, three-state input/output lines for the transfer of data, control and status information between the 82C50A and the CPU. For character formats of less than 8 bits, D7, D6 and D5 are "don't cares" for data write operations and 0 for data read operations. These lines are normally in a high impedance state except during read operations. D0 is the Least Significant Bit (LSB) and is the first serial data bit to be received or transmitted.                                                                                                                                                                            |  |

| A0, A1,<br>A2   | 28, 27,<br>26 |        | н               | REGISTER SELECT: The address lines select the internal registers during CPU bus operations. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

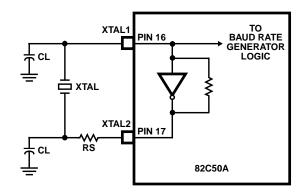

| XTAL1,<br>XTAL2 | 16<br>17      | I<br>O |                 | CRYSTAL/CLOCK: Crystal connections for the internal Baud Rate Generator. XTAL1 can also be used as an external clock input, in which case XTAL2 should be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SOUT            | 11            | 0      |                 | SERIAL DATA OUTPUT: Serial data output from the 82C50A transmitter circuitry. A Mark (1) is a logic one (high) and Space (0) is a logic zero (low). SOUT is held in the Mark condition when the transmitter is disabled, MR is true, the Transmitter Register is empty, or when in the Loop Mode. SOUT is not affected by the CTS input.                                                                                                                                                                                                                                                                                                                                    |  |

| GND             | 20            |        | L               | GROUND: Power supply ground connection (V <sub>SS</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| CTS             | 36            | I      | L               | CLEAR TO SEND: The logical state of the $\overline{\text{CTS}}$ pin is reflected in the CTS bit of the (MSR) Modem Status Register (CTS is bit 4 of the MSR, written MSR (4)). A change of state in the $\overline{\text{CTS}}$ pin since the previous reading of the MSR causes the setting of DCTS (MSR(O)) of the Modem Status Register. When $\overline{\text{CTS}}$ pin is ACTIVE (low), the modem is indicating that data on SOUT can be transmitted on the communications link. If $\overline{\text{CTS}}$ pin goes INACTIVE (high), the 82C50A should not be allowed to transmit data out of SOUT. $\overline{\text{CTS}}$ pin does not affect Loop Mode operation. |  |

| DSR             | 37            | I      | L               | DATA SET READY: The logical state of the DSR pin is reflected in MSR(5) of the Modem Status Register. DDSR (MSR(1)) indicates whether the DSR pin has changed state since the previous reading of the MSR. When the DSR pin is ACTIVE (low), the modem is indicating that it is ready to exchange data with the 82C50A, while the DSR Pin INACTIVE (high) indicates that the modem is not ready for data exchange. The ACTIVE condition indicates only the condition of the local Data Communications Equipment (DCE), and does not imply that a data circuit as been established with remote equipment.                                                                    |  |

| DTR             | 33            | Ο      | L               | DATA TERMINAL READY: The $\overline{\text{DTR}}$ pin can be set (low) by writing a logic 1 to MCR(0), Modem Control Register bit 0. This signal is cleared (high) by writing a logic 0 to the DTR bit (MCR(0)) or whenever a MR ACTIVE (high) is applied to the 82C50A. When ACTIVE (low), $\overline{\text{DTR}}$ pin indicates to the DCE that the 82C50A is ready to receive data. In some instances, $\overline{\text{DTR}}$ pin is used as a power on indicator. The INACTIVE (high) state causes the DCE to disconnect the modem from the telecommunications circuit.                                                                                                 |  |

| SYMBOL  | PIN<br>NUMBER | TYPE | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------|---------------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RTS     | 32            | Ο    | L               | REQUEST TO SEND: The $\overline{\text{RTS}}$ signal is an output used to enable the modem. The $\overline{\text{RTS}}$ pin is set low by writing a logic 1 to MCR (1) bit 1 of the Modem Control Regis ter. The $\overline{\text{RTS}}$ pin is reset high by Master Reset. When ACTIVE, the $\overline{\text{RTS}}$ pin indicates to the DCE that the 82C50A has data ready to transmit. In half duplex operations $\overline{\text{RTS}}$ is used to control the direction of the line.                                                                                                                                                                                                                                                                                                                                                                 |  |

| BAUDOUT | 15            | 0    |                 | BAUDOUT: This output is a 16X clock out used for the transmitter section (16X 16 times the data rate). The BAUDOUT clock rate is equal to the reference oscillate frequency divided by the specified divisor in the Baud Rate Generator Divisor Latch es DLL and DLM. BAUDOUT may be used by the Receiver section by tying this ou put to RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| OUT1    | 34            | 0    | L               | OUTPUT 1: This is a general purpose output that can be programmed ACTIVE<br>(low) by settingVCR(2) (OUT1) of the Modem Control Register to a high level. The<br>OUT1 pin is set high by Master Reset. The OUT1 pin is INACTIVE (high) during loop<br>mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| OUT2    | 31            | 0    | L               | OUTPUT 2: This is a general purpose output that can be programmed ACTIVE (low) by setting MCR(3) (OUT1) of the Modem Control Register to a high level. The OUT2 pin is set high by Master Reset. The OUT2 signal is INACTIVE (high) during loop mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RI      | 39            | 1    | L               | RING INDICATOR: When low, $\overline{RI}$ indicates that a telephone ringing signal has beer received by the modem or data set. The $\overline{RI}$ signal is a modem control input whose condition is tested by reading MSR(6) (RI). The Modem Status Register output TER (MSR(2)) indicates whether the $\overline{RI}$ input has changed from a Low to High since the previous reading of the MSR. If the interrupt is enabled (IER (3) = 1) and $\overline{RI}$ changes from a Low to High, an interrupt is generated. The ACTIVE (low) state of $\overline{RI}$ indicates that the DCE is receiving a ringing signal. $\overline{RI}$ will appear ACTIVE for approximately the same length of time as the ACTIVE segment of the ringing cycle. The INACTIVE state of $\overline{RI}$ will occur during the INACTIVE condition of $\overline{DTR}$ . |  |

| DCD     | 38            | I    | L               | DATA CARRIER DETECT: When ACTIVE (low), DCD indicates that the data carrie<br>has been detected by the modem or data set. DCD is a modem input whose condi-<br>tion can be tested by the CPU by reading MSR(7) (DCD) of the Modem Status Reg-<br>ister. MSR(3) (DDCD) of the Modem Status Register indicates whether the DCD<br>input has changed since the previous reading of the MSR. DOD has no effect on the<br>receiver. If the DCD changes state with the modem status interrupt enabled, an in-<br>terrupt is generated.<br>When DCD is ACTIVE (low), the received line signal from the remote terminal is<br>within the limits specified by the DCE manufacturer. The INACTIVE (high) signal in<br>dicates that the signal is not within the specified limits, or is not present.                                                               |  |

| MR      | 35            | 1    | Н               | MASTER RESET: The MR input forces the 82C50A into an idle mode in which a serial data activities are suspended. The Modem Control Register (MCR) along with its associated outputs are cleared. The Line Status Register (LSR) is cleared except for the THRE and TEMT bits, which are set. The 82C50A remains in an idle state until programmed to resume serial data activities. The MR input is a Schmitt trigger input. See the DC Electrical Characteristics for Schmitt trigger logic input voltage levels. See Table 7 for a summary of Master Reset's effect on 82C50A operation.                                                                                                                                                                                                                                                                |  |

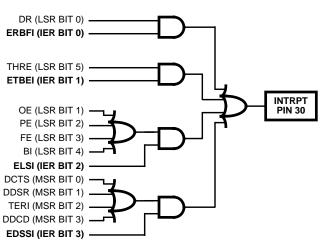

| INTRPT  | 30            | 0    | н               | INTERRUPT REQUEST: The INTRPT output goes ACTIVE (high) when one of the following interrupts has an ACTIVE (high) condition and is enabled by the Interrupt Enable Register: Receiver Error flag, Received Data Available, Transmitter Holding Register Empty, and Modem Status. The INTRPT is reset low upon appropriate service or a MR operation. See Figure 1. Interrupt Control Structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SIN     | 10            | I    | н               | SERIAL DATA INPUT: The SIN input is the serial data input from the communication line or modem to the 82C50A receiver circuits. A mark (1) is high, and a space (0 is low. Data inputs on SIN are disabled when operating in the loop mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Pin Description (Continued) |               |      |                 |                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------------|---------------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL                      | PIN<br>NUMBER | TYPE | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                |  |  |

| V <sub>CC</sub>             | 40            |      | Н               | $V_{CC}:~$ +5V positive power supply pin. A 0.1µA decoupling capacitor from $V_{CC}$ (pin 40) to GND (pin 20) is recommended.                                                                                                                                                                                                              |  |  |

| CS0, CS1,<br><u>CS2</u>     | 12,13,<br>14  |      | H, H,<br>L      | CHIP SELECT: The Chip Select inputs act as enable signals for the write (DOSTR, DOSTR) and read (DISTR, DISTR) input signals. The Chip Select inputs are latched by the ADS input.                                                                                                                                                         |  |  |

| NC                          | 29            |      |                 | Do Not Connect                                                                                                                                                                                                                                                                                                                             |  |  |

| CSOUT                       | 24            | 0    | Н               | CHIP SELECT OUT: When ACTIVE (high), this pin indicates that the chip has been selected by active CS0, CS1, and $\overline{CS2}$ inputs. No data transfer can be initiated unti CSOUT is a logic 1, ACTIVE (high).                                                                                                                         |  |  |

| DDIS                        | 23            | 0    | Н               | DRIVER DISABLE: This output is INACTIVE (low) when the CPU is reading data from the 82C50A. An ACTIVE (high) Dells output can be used to disable an externa transceiver when the CPU is reading data.                                                                                                                                      |  |  |

| ADS                         | 25            | I    | L               | ADDRESS STROBE: When ACTIVE (low), ADS latches the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) inputs. An active ADS is required when the Register Select pins are not stable for the duration of the read or write operation, multiplexed mode. If not required, the ADS input should be tied low, non-multiplexed mode. |  |  |

| RCLK                        | 9             | I    |                 | This input is the 16X Baud Rate Clock for the receiver section of the 82C50A. This input may be provided from the BAUDOUT output or an external clock.                                                                                                                                                                                     |  |  |

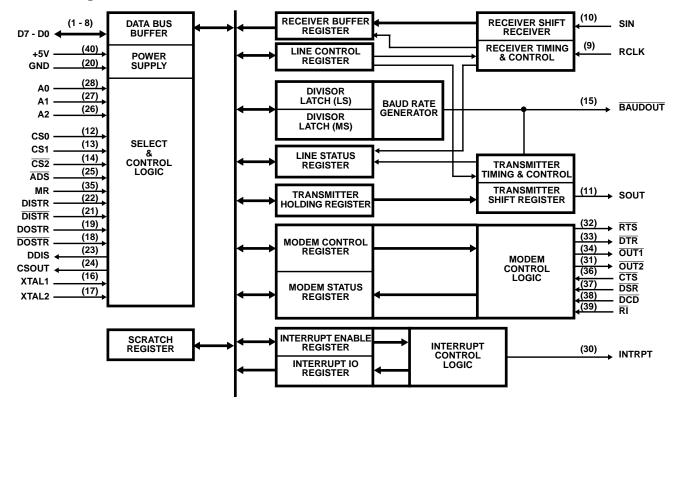

# Block Diagram

# Accessible Registers

The three types of internal registers in the 82C50A used in the operation of the device are control, status, and data registers. The control registers are the Bit Rate Select Register DLL and DLM, Line Control Register, Interrupt Enable Register and the Modem Control registers, while the status registers are the Line Status Registers and the Modem Status Register. The data registers are the Receiver Buffer Register and Transmitter Holding Register. The Address, Read, and Write inputs are used in conjunction with the Divisor Latch Access Bit in the Line Control Register (LCR(7)) to select the register to be written or read (see Table 1.). Individual bits within these registers are referred to by the register mnemonic and the bit number in parenthesis. An example, LCR(7) refers to Line Control Register Bit 7.

The Transmitter Buffer Register and Receiver Buffer Register are data registers holding from 5-8 data bits. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The 82C50A data registers are double buffered so that read and write operations can be performed at the same time the UART is performing the parallel to serial and serial to parallel conversion. This provides the microprocessor with increased flexibility in its read and write timing.

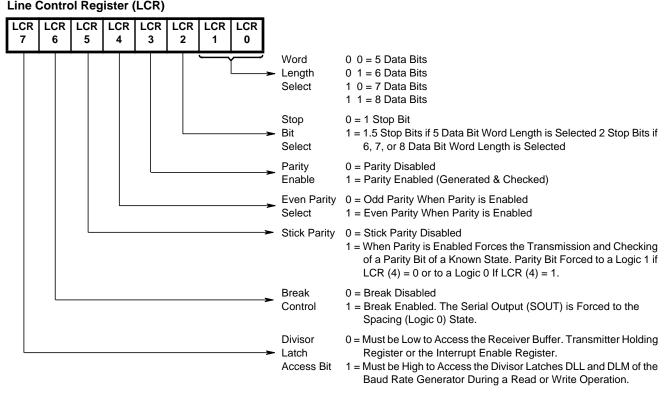

#### Line Control Register (LCR)

#### TABLE 1. ACCESSING 82C50A INTERNAL REGISTERS

| DLAB | A2 | A1 | A0 | MNEMONIC | REGISTER                                              |  |

|------|----|----|----|----------|-------------------------------------------------------|--|

| 0    | 0  | 0  | 0  | RBR      | Receiver Buffer<br>Register (read only)               |  |

| 0    | 0  | 0  | 0  | THR      | Transmitter Holding<br>Register (write only)          |  |

| 0    | 0  | 0  | 1  | IER      | Interrupt Enable<br>Register                          |  |

| Х    | 0  | 1  | 0  | IIR      | Interrupt Identifica-<br>tion Register<br>(read only) |  |

| Х    | 0  | 1  | 1  | LCR      | Line Control Register                                 |  |

| Х    | 1  | 0  | 0  | MCR      | Modem Control<br>Register                             |  |

| Х    | 1  | 0  | 1  | LSR      | Line Status Register                                  |  |

| Х    | 1  | 1  | 0  | MSR      | Modem Status<br>Register                              |  |

| Х    | 1  | 1  | 1  | SCR      | Scratch Register                                      |  |

| 1    | 0  | 0  | 0  | DLL      | Divisor Latch (LSB)                                   |  |

| 1    | 0  | 0  | 1  | DLM      | Divisor Latch (MSB)                                   |  |

#### LINE CONTROL REGISTER (LCR)

The format of the data character is controlled by the Line Control Register. The contents of the LCR may be read, eliminating the need for separate storage of the line characteristics in system memory. The contents of the LCR are described below.

#### LCR Bits 0 thru 7

- LCR (0) Word Length Select Bit 0 (WLS0)

- LCR (1) Word Length Select Bit 1 (WLS1)

- LCR (2) Stop Bit Select (STB)

- LOR (3) Parity Enable (PEN)

- LCR (4) Even Parity Select (EPS)

- LOR (5) Stick Parity

- LOR (6) Set Break

- LCR (7) Divisor Latch Access Bit (DLAB)

LCR(0) and LCR(1) Word Length Select Bit 0, Word Length Select Bit 1: The number of bits in each transmitted or received serial character is programmed as follows:

| LCR(1) | LCR(0) | WORD LENGTH |

|--------|--------|-------------|

| 0      | 0      | 5 Bits      |

| 0      | 1      | 6 Bits      |

| 1      | 0      | 7 Bits      |

| 1      | 1      | 8 Bits      |

**LCR(2)** Stop Bit Select: LCR(2) specifies the number of stop bits in each transmitted character. If LCR(2) is a logic 0, one stop bit is generated in the transmitted data. If LCR(2) is a logic 1 when a 5-bit word length is selected, 1.5 stop bits are generated. If LCR(2) is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, two stop bits are generated. The receiver checks for two stop bits if programmed.

**LCR(3)** Parity Enable: When LCR(3) is high, a parity bit between the last data word bit and stop bit is generated and checked.

**LCR(4) Even Parity Select:** When parity is enabled (LCR(3) = 1), LCR(4) = 0 selects odd parity, and LCR(4) = 1 selects even parity.

**LCR(5) Stick Parity:** When parity is enabled (LCR(3) = 1), LCR(5) = 1 causes the transmission and reception of a parity bit to be in the opposite state from that indicated by LCR(4). This allows the user to force parity to a known state and for the receiver to check the parity bit in a known state.

**LCR(6) Break Control:** When LCR(6) is set to logic-1, the serial output (SOUT) is forced to the spacing (logic 0) state. The break is disabled by setting LCR(6) to a logic-0. The Break Control bit acts only on SOUT and has no effect on the transmitter logic. Break Control enables the CPU to alert a terminal in a computer communications system. If the following sequence is used, no erroneous or extraneous characters will be transmitted because of the break.

- 1. Load an all Os pad character in response to THRE.

- 2. Set break in response to the next THRE.

- 3. Wait for the transmitter to be idle, (TEMT = 1), and clear break when normal transmission has to be restored.

During the break, the transmitter can be used as a character timer to accurately establish the break duration.

**LCR(7)** Divisor Latch Access Bit (DLAB): LCR(7) must be set high (logic 1) to access the Divisor Latches DLL and DLM of the Baud Rate Generator during a read or write operation. LCR(7) must be input low to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.

#### LINE STATUS REGISTER (LSR)

The LSR is a single register that provides status indications. The LSR is usually the first register read by the CPU to determine the cause of an interrupt or to poll the status of the 82C50A.

Three error flags OE, FE, and PE provide the status of any error conditions detected in the receiver circuitry. During reception of the stop bits, the error flags are set high by an error condition. The error flags are not reset by the absence of an error condition in the next received character. The flags reflect the last character only if no overrun occurred. The Overrun Error (OE) indicates that a character in the Receiver Buffer Register has been overwritten by a character from the Receiver Shift Register before being read by the CPU. The character is lost. Framing Error (FE) indicates that the last character received contained incorrect (low) stop bits. This is caused by the absence of the required stop bit or by a stop bit too short to be detected. Parity Error (PE) indicates that the last character received contained a parity error based on the programmed and calculated parity of the received character.

The Break Interrupt (BI) status bit indicates that the last character received was a break character. A break character is an invalid data character, with the entire character, including parity and stop bits, logic zero.

The Transmitter Holding Register Empty (THRE) bit indicates that the THR register is empty and ready to receive another character. The Transmission Shift Register Empty (TEMT) bit indicates that the Transmitter Shift Register is empty, and the 82C50A has completed transmission of the last character. If the interrupt is enabled (IER(1)), an active THRE causes an interrupt (INTRPT).

The Data Ready (DR) bit indicates that the RBR has been loaded with a received character (including Break) and that the CPU may access this data.

Reading the LSR clears LSR (1) - LSR (4). (OE, PE, FE and BI).

|     |     |                                              | LOGIC 1 | LOGIC 0   |

|-----|-----|----------------------------------------------|---------|-----------|

| LSR | (0) | Data Ready (DR)                              | Ready   | Not Ready |

| LSR | (1) | Overrun Error (OE)                           | Error   | No Error  |

| LSR | (2) | Parity Error (PE)                            | Error   | No Error  |

| LSR | (3) | Framing Error (FE)                           | Error   | No Error  |

| LSR | (4) | Break Interrupt (BI)                         | Break   | No Break  |

| LSR | (5) | Transmitter Holding<br>Register Empty (THRE) | Empty   | Not Empty |

| LSR | (6) | Transmitter Empty (TEMT)                     | Empty   | Not Empty |

| LSR | (7) | Not Used                                     |         |           |

The contents of the Line Status Register are indicated in the above table and are described below.

**LSR(0) Data Ready (DR):** Data Ready is set high when an incoming character has been received and transferred into the Receiver Buffer Register. LSR(0) is reset low by a CPU read of the data in the Receiver Buffer Register.

**LSR(1) Overrun Error (OE):** Overrun Error indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, overwriting the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register.

**LSR(2) Parity Error (PE):** Parity Error indicates that the received data character does not have the correct even or odd parity, as selected by the Even Parity Select bit (LCR (4)). The PE bit is set high upon detection of a parity error, and is reset low when the CPU reads the contents of the LSR.

**LSR(3)** Framing Error (FE): Framing Error indicates that the received character did not have a valid stop bit. LSR(3) is set high when the stop bit following the last data bit or parity bit is detected as a zero bit (spacing level). The FE indicator is reset low when the CPU reads the contents of the LSR.

**LSR(4) Break Interrupt (BI):** Break Interrupt is set high when the received data input is held in the spacing (logic 0) state for longer than a full word transmission time (start bit + data bits + parity + stop bits). The B indicator is reset when the CPU reads the contents of the Line Status Register.

**LSR(1)** - LSR(4) are the error conditions that produce a Receiver Line Status interrupt (priority 1 interrupt in the Interrupt Identification Register (IIR)) when any of the conditions are detected. This interrupt is enabled by setting IER (2) = 1 in the Interrupt Enable Register.

LSR(5) Transmitter Holding Register Empty (THRE): THRE indicates that the 82C50A is ready to accept a new character for transmission. The THRE bit is set high when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. LSR(5) is reset low by the loading of the Transmitter Holding Register by the CPU. LSR(5) is not reset by a CPU read of the LSR. When the THRE interrupt is enabled (IER(1) = 1), THRE causes a priority 3 interrupt in the IIR. If THRE is the interrupt source indicated in IIR, INTRPT is cleared by a read of the IIR.

**LSR(6)** Transmitter Empty (TEMT): TEMT is set high when the Transmitter Holding Register (THR) and the Transmitter Shift Register (TSR) are both empty. LSR(6) is reset low when a character is loaded into the THR and remains low until the character is transferred out of SOUT. TEMT is not reset low by a CPU read of the LSR.

**LSR(7):** This bit is permanently set to logic 0.

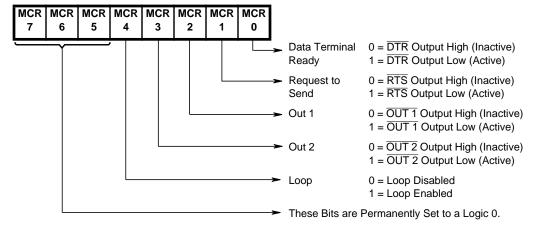

#### MODEM CONTROL REGISTER (MCR)

The MCR controls the interface with the modem or data set as described below. The MCR can be written and read. The  $\overline{\text{RTS}}$ ,  $\overline{\text{DTR}}$ ,  $\overline{\text{OUT1}}$  and  $\overline{\text{OUT2}}$  outputs are directly controlled by their control bits in this register. A high input asserts a low (true) at the output pins.

|     |     |                              | MCR BIT<br>LOGIC 1 | MCR BIT<br>LOGIC 0  |

|-----|-----|------------------------------|--------------------|---------------------|

| MCR | (0) | Data Terminal<br>Ready (DTR) | DTR<br>Output Low  | DTR<br>Output High  |

| MCR | (1) | Request to Send<br>(RTS)     | RTS<br>Output Low  | RTS<br>Output High  |

| MCR | (2) | OUT1                         | OUT1<br>Output Low | OUT1<br>Output High |

| MCR | (3) | OUT2                         | OUT2<br>Output Low | OUT2<br>Output High |

| MCR | (4) | LOOP                         | LOOP<br>Enabled    | LOOP<br>Disabled    |

| MCR | (5) | 0                            |                    |                     |

| MCR | (6) | 0                            |                    |                     |

| MCR | (7) | 0                            |                    |                     |

**MCR(0):** When MCR(0) is set high, the  $\overline{\text{DTR}}$  output is forced low. When MCR(0) is reset low, the  $\overline{\text{DTR}}$  output is forced high. The  $\overline{\text{DTR}}$  output of the 82C50A may be input into an EIA inverting line driver as the 1488 to obtain the proper polarity input at the modem or data set.

**MCR(1):** When MCR(1) is set high, the  $\overline{\text{RTS}}$  output is forced low. When MCR(1) is reset low, the  $\overline{\text{RTS}}$  output is forced high. The  $\overline{\text{RTS}}$  output of the 82C50A may be input into an EIA inverting line driver as the 1488 to obtain the proper polarity input at the modem or data set.

**MCR(2):** When MCR(2) is set high, the  $\overline{OUT1}$  output is forced low. When MCR(2) is reset low, the  $\overline{OUT1}$  output is forced high.  $\overline{OUT1}$  is an user designated output.

**MCR(3):** When MCR(3) is set high, the  $\overline{OUT2}$  output is forced low. When MCR(3) is reset low, the  $\overline{OUT2}$  output is forced high.  $\overline{OUT2}$  is an user designated output.

**MCR(4):** MCR(4) provides a local loopback feature for diagnostic testing of the 62C50A. When MCR(4) is set high,

Serial Output (SOUT) is set to the marking (logic 1) state, and the receiver data input Serial Input (SIN) is disconnected. The output of the Transmitter Shift Register is looped back into the Receiver Shift Register input. The four modem control inputs ( $\overline{\text{CTS}}$ ,  $\overline{\text{DSR}}$ , DC, and  $\overline{\text{RI}}$ ) are disconnected. The four modem control outputs ( $\overline{\text{DTR}}$ ,  $\overline{\text{RTS}}$ ,  $\overline{\text{OUT1}}$  and  $\overline{\text{OUT2}}$ ) are internally connected to the four modem control inputs. The modem control output pins are forced to their inactive state (high). In the diagnostic mode, data transmitted is immediately received. This allows the processor to verify the transmit and receive data paths of the 82C50A.

In the diagnostic mode, the receiver and transmitter interrupts are fully operational. The modem control interrupts are also operational, but the interrupt sources are now the lower four bits of the MCR instead of the four modem control inputs. The interrupts are still controlled by the Interrupt Enable Register.

MCR(5) - MCR(7): These bits are permanently set to logic 0.

#### Modem Control Register (MCR)

#### MODEM STATUS REGISTER (MSR)

The MSR provides the CPU with status of the modem input lines from the modem or peripheral device. The MSR allows the CPU to read the modem signal inputs by accessing the data bus interface of the 82C50A. In addition to the current status information, four bits of the MSR indicate whether the modem inputs have changed since the last reading of the MSR. The delta status bits are set high when a control input from the modem changes state, and reset low when the CPU reads the MSR.

The modem input lines are  $\overline{\text{CTS}}$  (pin 36),  $\overline{\text{DSR}}$  (pin 37),  $\overline{\text{RI}}$  (pin 39), and  $\overline{\text{DCD}}$  (pin 38). MSR(4) - MSR(7) are status indications of these lines. The status indications follow the status of the input lines. If the modem status interrupt in the Interrupt Enable Register is enabled (IER(3)), a change of state in a modem input signals will be reflected by the modem status bits in the IIR register, and an interrupt (INTRPT) is generated. The MSR is a priority 4 interrupt. The contents of the Modem Status Register are described below:

Note that the state (high or low) of the status bits are inverted versions of the actual input pins.

#### MSR BITS 0 THRU 7

| MSR BIT | MNEMONIC | DESCRIPTION                     |

|---------|----------|---------------------------------|

| MSR (1) | DDSR     | Delta Data Set Ready            |

| MSR (2) | TERI     | Trailing Edge of Ring Indicator |

| MSR (0) | DCTS     | Delta Clear To Send             |

| MSR (3) | DDCD     | Delta Data Carrier Detect       |

| MSR (4) | CTS      | Clear To Send                   |

| MSR (5) | DSR      | Data Set Ready                  |

| MSR (6) | RI       | Ring Indicator                  |

| MSR (7) | DCD      | Data Carrier Detect             |

**MSR(0) Delta Clear to Send (DCTS):** DCTS indicates that the  $\overline{\text{CTS}}$  input (Pin-36) to the 82C50A has changed state since the last time it was read by the CPU.

**MSR(1)** Delta Data Set Ready (DDSR): DDSR indicates that the  $\overline{\text{DSR}}$  input (Pin-37) to the 62C50A has changed state since the last time it was read by the CPU.

**MSR(2)** Trailing Edge of Ring Indicator (TERI): TERI indicates that the  $\overline{RI}$  input (Pin-39) to the 82C50A has Changed state from Low to High since the last time it was read by the CPU. High to Low transitions on  $\overline{RI}$  do not activate TERI.

**MSR(3)** Delta Data Carrier Detect (DDCD): DDCD indicates that the  $\overline{DCD}$  input (Pin-36) to the 82C50A has changed state since the last time it was read by the CPU.

**MSR(4) Clear to Send (CTS):** Clear to Send (CTS) is the status of the  $\overline{\text{CTS}}$  input (Pin-36) from the modem indicating to the 82C50A that the modem is ready to receive data from the 62C50A transmitter output (SOUT). If the 82C50A is in

the loop mode (MCR(4)=1), MSR(4) is equivalent to RTS in Check: the MCR.

**MSR(5)** Data Set Ready (DSR): Data Set Ready (DSR) is a status of the  $\overline{\text{DSR}}$  input (Pin-37) from the modem to the 82C50A which indicates that the modem is ready to provide received data to the 82C50A receiver circuitry. If the 82C50A is in the loop mode (MCR(4) = 1), MSR(5) is equivalent to DTR in the MCR.

**MSR(6) Ring Indicator MSR(6):** Indicates the status of the RI input (Pin-39). If the 82C50A is in the loop mode (MCR(4) = 1), MSR(6) is equivalent to OUT1 in the MCR.

**MSR(7)** Data Carrier Detect (MSR(7)): Data Carrier Detect indicates the status of the Data Carrier Detect (DCD) input (Pin-38). If the 82C50A is in the loop mode (MCR(4) = 1), MSR(4) is equivalent to OUT2 of the MCR.

The modem status inputs (RI, DCD, DSR and CTS) reflect the modem input lines with any change of status. **Reading the MSR register will clear the delta modem status indications but has no effect on the status bits.** The status bits reflect the state of the input pins regardless of the mask control signals. If a DCTS, DDSR, TERI, or DDCD are true and a state change occurs during a read operation (DISTR, DISTR), the state change is not indicated in the MSR. If DCTS, DDSR, TERI, or DDCD are false and a state change occurs during a read operation, the state change is indicated after the read operation.

For LSR and MSR, the setting of status bits is inhibited during status register read (DISTR, DISTR) operations. If a status condition is generated during a read (DISTR, DISTR) operation, the status bit is not set until the trailing edge of the read (DISTR, DISTR).

If a status bit is set during a read (DISTR, DISTR) operation, and the same status condition occurs, that status bit will be cleared at the trailing edge of the read (DISTR, DISTR) instead of being set again.

#### BAUD RATE SELECT REGISTER (BRSR)

The 82C50A contains a programmable Baud Rate Generator (BRG) that divides the clock (DC to 10MHz) by any divisor from 1 to  $2^{16}$ -1 (see also BRG description). The output frequency of the Baud Generator is 16X the data rate [divisor # = frequency input ÷ (baud rate x 16)]. **Two 8-bit divisor latch registers store the divisor in a 16-bit binary format.** These Divisor Latch registers must be loaded during initialization. Upon loading either of the Divisor Latches, a 16-bit Baud counter is immediately loaded. This prevents long counts on initial load.

Sample Divisor Number Calculation:

| Given:   | Desired Baud Rate 1200 Baud<br>Frequency Input 1.8432MHz                            |

|----------|-------------------------------------------------------------------------------------|

| Formula: | Divisor # = Frequency Input ÷ (Baud Rate x 16)<br>Divisor # = 1843200 ÷ (1200 x 16) |

| Answer:  | Divisor # = $96 = 60_{HEX} \rightarrow DLL = 01100000$<br>DLM = 00000000            |

The Divisor # 96 will divide the input frequency 1.8432MHz down to 19200 which is 16 times the desired baud rate.

#### **Divisor Latch Least Significant BYTE**

| DLL (0) | Bit 0 |

|---------|-------|

| DLL (1) | Bit 1 |

| DLL (2) | Bit 2 |

| DLL (3) | Bit 3 |

| DLL (4) | Bit 4 |

| DLL (5) | Bit 5 |

| DLL (6) | Bit 6 |

| DLL (7) | Bit 7 |

#### **Divisor Latch Most Significant BYTE**

| DLM (0) | Bit 8  |

|---------|--------|

| DLM (1) | Bit 9  |

| DLM (2) | Bit 10 |

| DLM (3) | Bit 11 |

| DLM (4) | Bit 12 |

| DLM (5) | Bit 13 |

| DLM (6) | Bit 14 |

| DLM (7) | Bit 15 |

#### **RECEIVER BUFFER REGISTER (RBR)**

The receiver circuitry in the 82C50A is programmable for 5, 6, 7 or 8 data bits per character. For words of less than 8 bits, the data is right justified to the least significant bit (LSB = Data Bit 0 (RBR(0)). Data Bit 0 of a data word (RBR(0)) is the first data bit received. The unused bits in a character less than 8 bits are output low to the parallel output by the 82C50A.

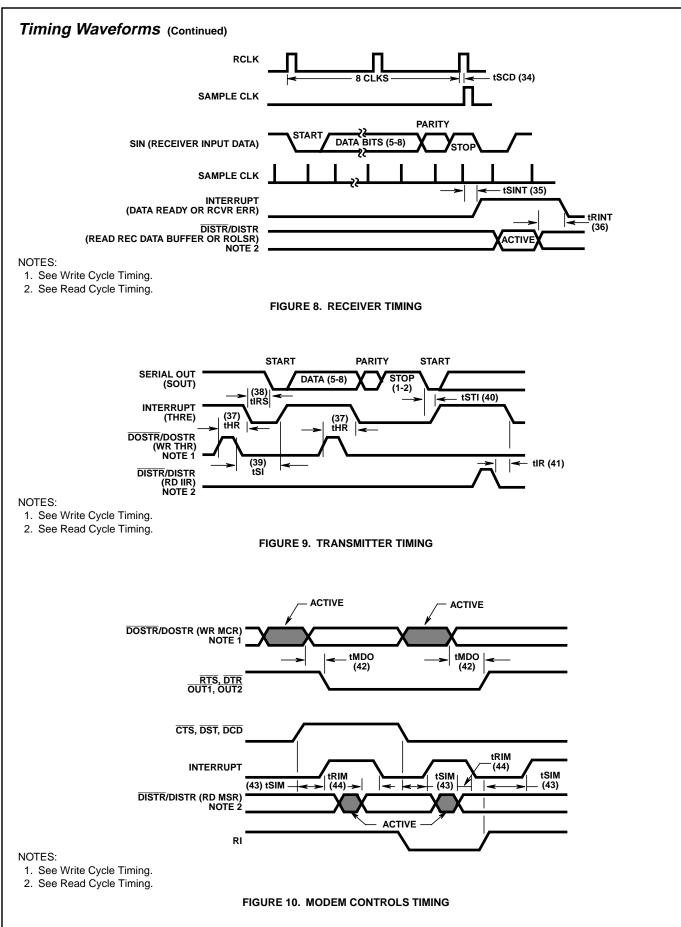

Received data at the SIN input pin is shifted into the Receiver Shift Register by the 16X clock provided at the RCLK input. This clock is synchronized to the incoming data based on the position of the start bit. When a complete character is shifted into the Receiver Shift Register, the assembled data bits are parallel loaded into the Receiver Buffer Register. The DR flag in the LSR register is set.

Double buffering of the received data permits continuous reception of data without losing received data. While the Receiver Shift Register is shifting a new character into the 82C50A, the Receiver Buffer Register is holding a previously received character for the CPU to read. Failure to read the data in the RBR before complete reception of the next character result in the loss of the data in the Receiver Register. The OE flag in the LSR register indicates the overrun condition.

#### RBR Bits 0 thru 7

| RBR (0) | Data Bit 0 |

|---------|------------|

| RBR (1) | Data Bit 1 |

| RBR (2) | Data Bit 2 |

| RBR (3) | Data Bit 3 |

| RBR (4) | Data Bit 4 |

| RBR (5) | Data Bit 5 |

| RBR (6) | Data Bit 6 |

| RBR (7) | Data Bit 7 |

|         |            |

#### TRANSMITTER HOLDING REGISTER (THR)

The Transmitter Holding Register (THR) holds parallel data from the data bus (D0-D7) until the Transmitter Shift Register is empty and ready to accept a new character for transmission. The transmitter and receiver word length and number of stop bits are the same. If the character is less than eight bits, unused bits at the microprocessor data bus are ignored by the transmitter.

Data Bit 0 (THR(0)) is the first serial data bit transmitted. The THRE flag (LSR(5)) reflect the status of the THR. The TEMT flag (LSR(6)) indicates if both the THR and TSR are empty.

#### THR Bits 0 thru 7

| THR (0) | Data Bit 0 |

|---------|------------|

| THR (1) | Data Bit 1 |

| THR (2) | Data Bit 2 |

| THR (3) | Data Bit 3 |

| THR (4) | Data Bit 4 |

| THR (5) | Data Bit 5 |

| THR (6) | Data Bit 6 |

| THR (7) | Data Bit 7 |

#### SCRATCHPAD REGISTER (SCR)

This 8-bit Read/Write register has no effect on the 82C50A. It is intended as a scratchpad register to be used by the programmer to hold data temporarily.

#### SCR Bits 0 thru 7

| SCR (0) | Data Bit 0 |

|---------|------------|

| SCR (1) | Data Bit 1 |

| SCR (2) | Data Bit 2 |

| SCR (3) | Data Bit 3 |

| SOR (4) | Data Bit 4 |

| SCR (5) | Data Bit 5 |

| SOR (6) | Data Bit 6 |

| SCR (7) | Data Bit 7 |

|         |            |

### Interrupt Structure

#### **INTERRUPT IDENTIFICATION REGISTER (IIR)**

The 82C50A has interrupt capability for interfacing to current microprocessors. In order to minimize software overhead during data character transfers, the 82C50A prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows:

- 1. Receiver Line Status (Priority 1)

- 2. Received Data Ready (Priority 2)

- 3. Transmitter Holding Register Empty (Priority 3)

- 4. Modem Status (Priority 4).

Information indicating that a prioritized interrupt is pending and the type of interrupt is stored in the Interrupt Identification Register (IIR). When addressed during chip select time, the IIR indicates the highest priority interrupt pending. No other interrupts are acknowledged until the interrupt is serviced by the CPU. The contents of the IIR are indicated in Table 2 and are described below.

**IIR(0):** IIR(0) can be used in either a hardwired prioritized or polled environment to indicate whether an interrupt is pending. When IIR(0) is low, an interrupt is pending, and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When IIR(0) is high, no interrupt is pending.

**IIR(1) and IIR(2):** IIR(1) and IIR(2) are used to identify the highest priority interrupt pending as indicated in Table 2.

**IIR(3) - IIR(7):** These five bits of the IIR are logic 0.

#### TABLE 2. INTERRUPT IDENTIFICATION REGISTER

|       | INTERRUPT IDENTIFICATION |       |                   | INTERRU                    | JPT SET AND RES            | ET FUNCTIONS                                                |

|-------|--------------------------|-------|-------------------|----------------------------|----------------------------|-------------------------------------------------------------|

| BIT 2 | BIT 1                    | BIT 0 | PRIORITY<br>LEVEL | INTERRUPT<br>FLAG          | INTERRUPT<br>SOURCE        | INTERRUPT<br>RESET CONTROL                                  |

| Х     | Х                        | 1     |                   | None                       | None                       |                                                             |

| 1     | 1                        | 0     | First             | Receiver Line<br>Status    | OE, PE, FE, or<br>BI       | LSR Read                                                    |

| 1     | 0                        | 0     | Second            | Received Data<br>Available | Receiver Data<br>Available | RBR Read                                                    |

| 0     | 1                        | 0     | Third             | THRE                       | THRE                       | IIR Read if THRE is the<br>Interrupt Source or<br>THR Write |

| 0     | 0                        | 0     | Fourth            | Modem Status               | CTS, DSR, RI,<br>DCD       | MSR Read                                                    |

NOTE: X = Not Defined, May Be 0 or 1

#### **INTERRUPT ENABLE REGISTER (IER)**

The Interrupt Enable Register (IER) is a Write register used to independently enable the four 82C50A interrupts which activate the interrupt (INTRPT) output. All interrupts are disabled by resetting IER(0) - IER(3) of the Interrupt Enable

Register. Interrupts are enabled by setting the appropriate bits of the IER high. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INTRPT output. All other system functions operate in their normal manner, including the setting of the Line Status and **IER(0):** When programmed high (IER(0) = Logic 1), IER(0) enables Received Data Available interrupt.

**IER(1):** When programmed high (IER(1) = Logic 1), IER(1) enables the Transmitter Holding Register Empty interrupt.

**IER(2):** When Programmed high (IER(2) = Logic 1), IER(2) enables the Receiver Line Status interrupt.

**IER(3):** When programmed high (IER(3) = Logic 1), IER(3) enables the Modern Status interrupt.

**IER(4) - IER(7):** These four bits of the IER are logic 0.

FIGURE 1. 82C50A INTERRUPT CONTROL STRUCTURE

| TABLE 3. 82C50A ACCESSIBLE REGISTER SUMMARY            |  |

|--------------------------------------------------------|--|

| (NOTE: See Table 1 for how to access these registers.) |  |

| REGISTER            | REGISTER BIT NUMBER                         |                                |                                                       |                                |                                                   |                                                             |                                                                               |                                                                 |

|---------------------|---------------------------------------------|--------------------------------|-------------------------------------------------------|--------------------------------|---------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|

| MNEMONIC            | BIT 7                                       | BIT 6                          | BIT 5                                                 | BIT 4                          | BIT 3                                             | BIT 2                                                       | BIT 1                                                                         | BIT 0                                                           |

| RBR<br>(Read Only)  | Data Bit 7<br>(MSB)                         | Data Bit 6                     | Data Bit 5                                            | Data Bit 4                     | Data Bit 3                                        | Data Bit 2                                                  | Data Bit 1                                                                    | Data Bit 0<br>(LSB)†                                            |

| THR<br>(Write Only) | Data Bit 7                                  | Data Bit 6                     | Data Bit 5                                            | Data Bit 4                     | Data Bit 3                                        | Data Bit 2                                                  | Data Bit 1                                                                    | Data Bit 0                                                      |

| DLL                 | Bit 7                                       | Bit 6                          | Bit 5                                                 | Bit 4                          | Bit 3                                             | Bit 2                                                       | Bit 1                                                                         | Bit 0                                                           |

| DLM                 | Bit 15                                      | Bit 14                         | Bit 13                                                | Bit 12                         | Bit 11                                            | Bit 10                                                      | Bit 9                                                                         | Bit 8                                                           |

| IER                 | 0                                           | 0                              | 0                                                     | 0                              | (EDSSI)<br>Enable<br>Modem<br>Status<br>Interrupt | (ELSI)<br>Enable<br>Receiver<br>Line<br>Status<br>Interrupt | (ETBEI)<br>Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt | (ERBFI)<br>Enable<br>Received<br>Data<br>Available<br>Interrupt |

| IIR<br>(Read Only)  | 0                                           | 0                              | 0                                                     | 0                              | 0                                                 | Interrupt ID<br>Bit (1)                                     | Interrupt ID<br>Bit (0)                                                       | "0" 1F<br>Interrupt<br>Pending                                  |

| LCR                 | (DLAB)<br>Divisor<br>Latch<br>Access<br>Bit | Set Break                      | Stick Parity                                          | (EPS)<br>Even Parity<br>Select | (PEN)<br>Parity<br>Enable                         | (STB)<br>Number<br>of Stop<br>Bits                          | (WLSB1)<br>Word<br>Length<br>Select<br>Bit 1                                  | (WLSB0)<br>Word<br>Length<br>Select<br>Bit 0                    |

| MCR                 | 0                                           | 0                              | 0                                                     | Loop                           | Out 2                                             | Out 1                                                       | (RTS)<br>Request<br>to Send                                                   | (DTR)<br>Data<br>Terminal<br>Ready                              |

| LSR                 | 0                                           | (TEMT)<br>Transmitter<br>Empty | (THRE)<br>Transmitter<br>Holding<br>Register<br>Empty | (BI)<br>Break<br>Interrupt     | (FE)<br>Framing<br>Error                          | (PE)<br>Parity<br>Error                                     | (OE)<br>Overrun<br>Error                                                      | (DR)<br>Data<br>Ready                                           |

| MSR                 | (DCD)<br>Data<br>Carrier<br>Detect          | (RI)<br>Ring<br>Indicator      | (DSR)<br>Data<br>Set<br>Ready                         | (CTS)<br>Clear<br>to<br>Send   | (DDCD)<br>Delta<br>Data<br>Carrier<br>Detect      | (TERI)<br>Trailing<br>Edge<br>Ring<br>Indicator             | (DDSR)<br>Delta<br>Data<br>Set<br>Ready                                       | (DCTS)<br>Delta<br>Clear<br>to<br>Send                          |

| SCR                 | Bit 7                                       | Bit 6                          | Bit 5                                                 | Bit 4                          | Bit 3                                             | Bit 2                                                       | Bit 1                                                                         | Bit 0                                                           |

$\dagger \text{LSB},$  Data Bit 0 is the first bit transmitted or received.

#### Transmitter

The serial transmitter section consists of a Transmitter Holding Register (THR), Transmitter Shift Register (TSR), and associated control logic. The Transmitter Holding Register Empty (THRE) and Transmitter Shift Register Empty (TEMT) are two bits in the Line Status Register which indicate the status of THR and TSR. To transmit a 5-8 bit word, the word is written through D0-D7 to the THR. The microprocessor should perform a write operation only if THRE is high. The THRE is set high when the word is automatically transferred from the THR to the TSR during the transmission of the start bit.

When the transmitter is idle, both THRE and TEMT are high. The first word written causes THRE to be reset to 0. After completion of the transfer, THRE returns high. TEMT remains low for at least the duration of the transmission of the data word. If a second character is transmitted to the THR, the THRE is reset low. Since the data word cannot be transferred from the THR to the TSR until the TSR is empty, THRE remains low until the TSR has completed transmission of the word. When the last word has been transmitted out of the TSR, TEMT is set high. THRE is set high one THR to TSR transfer time later.

#### Receiver

Serial asynchronous data is input into the SIN pin. The idle state of the line providing the input into SIN is high. A start bit detect circuit continually searches for a high to low transition from the idle state. When the transition is detected, a counter is reset, and counts the 16X clock to 7 1/2, which is the center of the start bit. The start bit is valid if the SIN is still low at the mid bit sample of the start bit. Verifying the start bit prevents the receiver from assembling an incorrect data character due to a low going noise spike on the SIN input.

The Line Control Register determines the number of data bits in a character (LCR(0), LCR(1)), number of stop bits LCR(2), if parity is used LCR(3), and the polarity of parity LCR(4). Status information for the receiver is provided in the Line Status Register. When a character is transferred from the Receiver Shift Register to the Receiver Buffer Register, the Data Received indication in LSR(0) is set high. The CPU reads the Receiver Buffer Register through D0-D7. This read resets LSR(0). If D0-D7 are not read prior to a new character transfer from the RSR to the RBR, the overrun error status indication is set in LSR(1). The parity check tests for even or odd parity on the parity bit, which precedes the first stop bit. If there is a parity error, the parity error is set in LSR (2). There is circuitry which tests whether the stop bit is high. If it is not, a framing error indication is generated in LSR(3).

The center of the start bit is defined as clock count 7 1/2. If the data into SIN is a symmetrical square wave, the center of the data cells will occur within  $\pm 3.125\%$  of the actual center, providing an error margin of 46.875%. The start bit can begin as much as one 16X clock cycle prior to being detected.

#### **Baud Rate Generator (BRG)**

The BRG generates the clocking for the UART function, providing standard ANSI/CCITT bit rates. The oscillator driving the BRG may be provided either with the addition of an external crystal to the XTAL1 and XTAL2 inputs, or an external clock into XTAL1. In either case, a buffered clock output, BAUDOUT, is provided for other system clocking. If two 82C50As are used on the same board, one can use a crystal, and the buffered clock output can be routed directly into the XTAL1 of the second 82C50A.

The data rate is determined by the Divisor Latch registers DLL and DLM and the external frequency or crystal input, with the  $\overline{BAUDOUT}$  providing an output 16X the data rate. The bit rate is selected by programming the two divisor latches, Divisor Latch Most Significant Byte and Divisor Latch Least Significant Byte. Setting DLL = 1 and DLM = 0 selects the divisor to divide by 1 (divide by 1 gives maximum baud rate for a given input frequency at XTAL1). The on-chip oscillator is optimized for a 10MHz crystal. Usually, higher frequency are less expensive than lower frequency crystals.

The BRG can use any of three different popular crystals to provide standard baud rates. The frequency of these three common crystals on the market are 1.8432MHz, 2.4576MHz, and 3.072MHz. With these standard crystals, standard bit rates from 50 to 38.5kbps are available. The following tables illustrate the divisors needed to obtain standard rates using these three crystal frequencies.

| TABLE 4. | <b>BAUD RATES</b> | USING 1.8432MHz | CRYSTAL |

|----------|-------------------|-----------------|---------|

|----------|-------------------|-----------------|---------|

| DESIRED<br>BAUD<br>RATE | DIVISOR USED TO<br>GENERATE<br>16 x CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|-------------------------|-------------------------------------------|-----------------------------------------------------------|

| 50                      | 2304                                      | -                                                         |

| 75                      | 1536                                      | -                                                         |

| 110                     | 1047                                      | 0.026                                                     |

| 134.5                   | 857                                       | 0.058                                                     |

| 150                     | 768                                       | -                                                         |

| 300                     | 384                                       | -                                                         |

| 600                     | 192                                       | -                                                         |

| 1200                    | 96                                        | -                                                         |

| 1800                    | 64                                        | -                                                         |

| 2000                    | 58                                        | 0.69                                                      |

| 2400                    | 48                                        | -                                                         |

| 3600                    | 32                                        | -                                                         |

| 4800                    | 24                                        | -                                                         |

| 7200                    | 16                                        | -                                                         |

| 9600                    | 12                                        | -                                                         |

| 19200                   | 6                                         | -                                                         |

| 38400                   | 3                                         | -                                                         |

| 56000                   | 2                                         | 2.86                                                      |

| · · · · · · · · · · · · · · · · · · · |                                           |                                                           |  |  |  |  |  |

|---------------------------------------|-------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| DESIRED<br>BAUD<br>RATE               | DIVISOR USED TO<br>GENERATE<br>16 x CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |  |  |  |  |  |

| 50                                    | 3072                                      | -                                                         |  |  |  |  |  |

| 75                                    | 2048                                      | -                                                         |  |  |  |  |  |

| 110                                   | 1396                                      | 0.026                                                     |  |  |  |  |  |

| 134.5                                 | 1142                                      | 0.0007                                                    |  |  |  |  |  |

| 150                                   | 1024                                      | -                                                         |  |  |  |  |  |

| 300                                   | 512                                       | -                                                         |  |  |  |  |  |

| 600                                   | 256                                       | -                                                         |  |  |  |  |  |

| 1200                                  | 128                                       | -                                                         |  |  |  |  |  |

| 1800                                  | 85                                        | 0.392                                                     |  |  |  |  |  |

| 2000                                  | 77                                        | 0.260                                                     |  |  |  |  |  |

| 2400                                  | 64                                        | -                                                         |  |  |  |  |  |

| 3600                                  | 43                                        | 0.775                                                     |  |  |  |  |  |

| 4800                                  | 32                                        | -                                                         |  |  |  |  |  |

| 7200                                  | 21                                        | 1.587                                                     |  |  |  |  |  |

| 9600                                  | 16                                        |                                                           |  |  |  |  |  |

| 19200                                 | 8                                         | -                                                         |  |  |  |  |  |

| 38400                                 | 4                                         | -                                                         |  |  |  |  |  |

#### TABLE 5. BAUD RATES USING 2.4576MHz CRYSTAL

#### DESIRED **DIVISOR USED TO** PERCENT ERROR BAUD GENERATE DIFFERENCE BETWEEN RATE DESIRED AND ACTUAL 16 x CLOCK 50 3840 75 2560 -110 1745 0.026 134.5 1428 0.034 150 1280 \_ 640 300 -600 320 -1200 160 -1800 107 0.312 2000 96 -2400 80 -3600 53 0.628 4800 40 -7200 27 1.23 9600 20 -19200 10 \_ 5 38400 -

TABLE 6. BAUD RATES USING 3.072MHz CRYSTAL

#### Reset

After powerup, the 82C50A Master Reset Schmitt trigger input (MR) should be held high for TMRW ns to reset the 82C50A circuits to an idle mode until initialization. A high on MR causes the following:

- 1. Initializes the transmitter and receiver internal clock counters.

- Clears the Line Status Register (LSR), except for Transmitter Shift Register Empty (TE MT) and Transmit Holding Register Empty (THRE), which are set. The Modem Control Register (MCR) is also cleared. All of the discrete lines, memory elements and miscellaneous

logic associated with these register bits are also cleared or turned off. Divisor Latches, Receiver Buffer Register, Transmitter Buffer Register are not effected.

Following removal of the reset condition (MR low), the 82C50A remains in the idle mode until programmed.

A hardware reset of the 82C50A sets the THRE and TEMT status bit in the LSR. When interrupts are subsequently enabled, an interrupt occurs due to THRE.

A summary of the effect of a Master Reset on the 82C50A is given in Table 7.

| REGISTER/SIGNAL                   | RESET CONTROL         | RESET                                                           |

|-----------------------------------|-----------------------|-----------------------------------------------------------------|

| Interrupt Enable Register         | Master Reset          | All Bits Low (0-3 forced and 4-7 permanent)                     |

| Interrupt Identification Register | Master Reset          | Bit 0 is High, Bits 1 and 2 Low Bits 3-7 are<br>Permanently Low |

| Line Control Register             | Master Reset          | All Bits Low                                                    |

| MODEM Control Register            | Master Reset          | All Bits Low                                                    |

| Line Status Register              | Master Reset          | All Bits Low, Except Bits 5 and 6 are High                      |

| MODEM Status Register             | Master Reset          | Bit 0-3 Low Bits 4-7 Input Signal                               |

| SOUT                              | Master Reset          | High                                                            |

| Intrpt (RCVR Errs)                | Read LSR/MR           | Low                                                             |

| Intrpt (RCVR Data Ready)          | Read RBR/MR           | Low                                                             |

| Intrpt (THRE)                     | Read IIR/Write THR/MR | Low                                                             |