| Instruction set design               |                                                                             |

|--------------------------------------|-----------------------------------------------------------------------------|

| Instruction set p                    | arameters (I)                                                               |

|                                      |                                                                             |

| • What to be taken into account      | t when decigning instruction acts                                           |

| What to be taken into account        | t when designing instruction sets                                           |

|                                      |                                                                             |

|                                      |                                                                             |

| What to take into account            | Related to                                                                  |

| CPU operands storage                 | Locations to storage operands: main                                         |

| Fundinit an annual annu in struction | memory, registers,                                                          |

| Explicit operands per instruction    | How many operands are designated in<br>an instruction                       |

| Operand location                     | Can ALU operate with memory                                                 |

|                                      | operands?                                                                   |

| Operations                           | How is a memory address specified?<br>What operations are considered by the |

| Operations                           | instruction set?                                                            |

| Operand sizes and types              | How is each operand specified?                                              |

|                                      | Which are operand sizes and types?                                          |

|                                      | Which are operand sizes and types :                                         |

|                                      |                                                                             |

|                                      |                                                                             |

| Less | son 2:                                      |                                                         |                                | Slide: 8 / 54                                                                                    |

|------|---------------------------------------------|---------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------|

|      | Instruction set des<br>Instructi<br>Outside | on set p                                                |                                | ers (II).<br>Iternatives                                                                         |

|      | Temporal E<br>storage                       | xplicit operands<br>per ALU<br>instruction              | Target result                  | t Accessing to explicit<br>operands                                                              |

|      | Stack machine                               | 0                                                       | Stack                          | Push / Pop                                                                                       |

|      | Accumulator<br>machine                      | 1                                                       | Accumulator                    | Accumulator Load / Store                                                                         |

|      | Register file<br>machine                    | 2 or 3                                                  | Registers or<br>memory address | Register or memory addresses<br>load / store                                                     |

|      | Machine type                                | Advantages                                              |                                | Drawbacks                                                                                        |

|      | Stack machine                               | Useful to evalua<br>Good density co<br>instructions are | de moreover                    | Impossible random stack access<br>Difficulty for efficient code<br>generation and implementation |

|      | Accumulator machine                         | Minimizes interr                                        | nal state machine              | A lot of traffic between accumulator and memory                                                  |

|      | Register file machine                       |                                                         | t code generation              | Long instructions to name registers                                                              |

| )n   | Automatic Departmen                         | t Graduate in (                                         |                                | Computers Structure and Organization.<br>es / Graduate in Computer Engineering                   |

|     |                | ion set p         |           | nete      | rs (V     | ).            |

|-----|----------------|-------------------|-----------|-----------|-----------|---------------|

| N   | lemory         | address           | sing      |           |           |               |

| _   |                |                   |           |           |           |               |

|     |                | nory address inte | erpretate | ed? Byte  | , half wo | rd, word,     |

| C   | louble word    |                   |           |           |           |               |

| • 1 | There two wa   | vs to storage the | e bytes o | of a word | l in mem  | orv depending |

|     |                | xxxx00 byte a     |           |           |           | 2             |

|     |                | 00450701 104      |           | 1.5       | 0.01      |               |

| • 3 | 32 DIts word 1 | 2345678h is to    | be store  | a from 1  | uun mer   | nory address. |

|     |                |                   |           |           |           |               |

|     | Addresses      |                   | 100h      | 101h      | 102h      | 103h          |

|     | Content        | Little endian     | 78        | 56        | 34        | 12            |

|     | contonio       | Big endian        | 12        | 34        | 56        | 78            |

|     |                |                   |           |           |           |               |

|     |                |                   |           |           |           |               |

|     |                |                   |           |           |           |               |

|   | <sup>1 2:</sup><br>struction set design<br>Instruction s<br>Memory add |                            | Slide: 13 / 5         |

|---|------------------------------------------------------------------------|----------------------------|-----------------------|

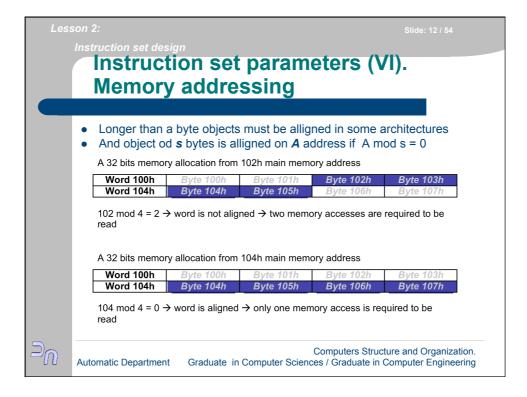

|   | A non-alligned memory                                                  | access has several         | memory references     |

|   | · · · · · · · · · · · · · · · · · · ·                                  |                            | ,                     |

| • | <ul> <li>Even non required allig<br/>alligned memory refere</li> </ul> | nement machines a<br>ences | re faster in accessig |

| • | Aligned and non-alligned                                               | ed different object siz    | zes examples:         |

|   | Addressed object                                                       | Byte aligned               | Non byte aligned      |

|   | Byte (8 bits)                                                          | 0, 1, 2, 3, 4, 5, 6, 7     | Never                 |

|   | Half word (16 bits)                                                    | 0, 2, 4, 6                 | 1, 3, 5, 7            |

|   | Word (32 bits)                                                         | 0, 4                       | 1, 2, 3, 5, 6, 7      |

|   | Double word (64 bits)                                                  | 0                          | 1, 2, 3, 4, 5, 6, 7   |

.esson 2:

## Instruction formats (IV). Instruction coding

## • General characteristics:

- Systematic format: fields use fixed positions.

- Operation code: or its extension is the first field

- They are multiple of the computer word: for memory access optimization

- Instruction format alternatives:

- Fixed format: it's very difficult to implement it because it uses the same format for all instruction types

- Variable format: operation code, extended operation codes, variable number of operands and different addressing modes are used

- Mixed format : two or three fixed format are use to fit instructions

- Orthogonal format: whatever instruction may use whatever operand and whatever addressing mode

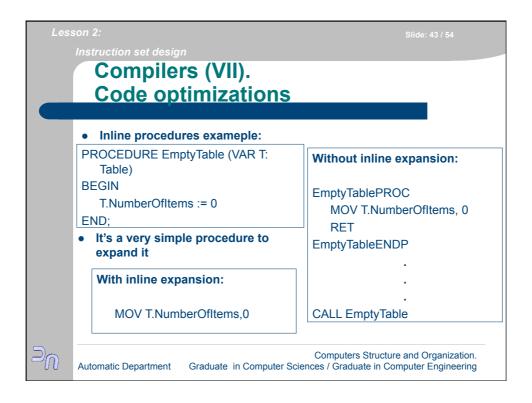

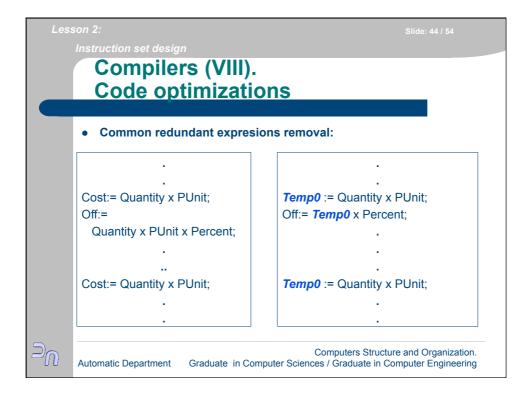

| Less                    | son 2:                                                                                                          | Slide: 42 / 54                                                                                                                        |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | Instruction set design                                                                                          |                                                                                                                                       |  |  |

|                         | Compilers (<br>Code optim                                                                                       |                                                                                                                                       |  |  |

|                         | Optimization                                                                                                    | Description                                                                                                                           |  |  |

|                         | Inline procedures<br>Common redundant sub<br>expression removal                                                 | To decide if a procedure is expanded inline or not<br>To substitute two or more copies of the same calculus by a<br>temporal variable |  |  |

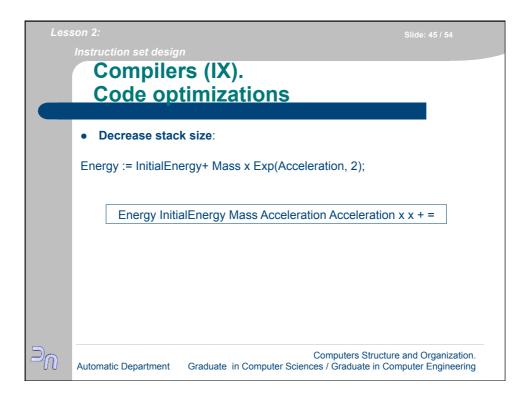

|                         | Decrease size of the stack                                                                                      | To reorder operands to push in order of having less stack acceses                                                                     |  |  |

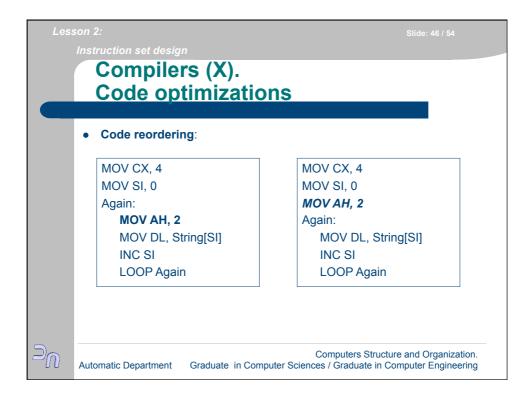

|                         | Code reordering                                                                                                 | To remove a transfer instruction with the same value which<br>may be inside a loop                                                    |  |  |

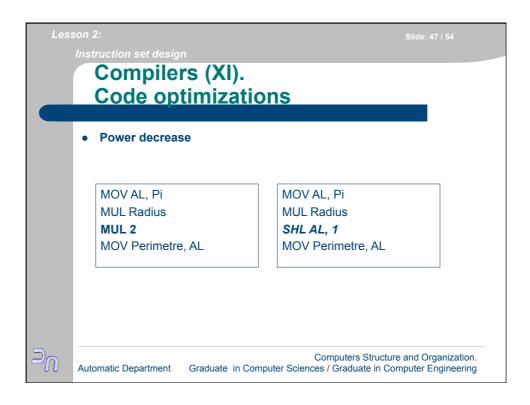

|                         | Power decrease                                                                                                  | To substitute multiplications by additions and divisions by<br>subtractions                                                           |  |  |

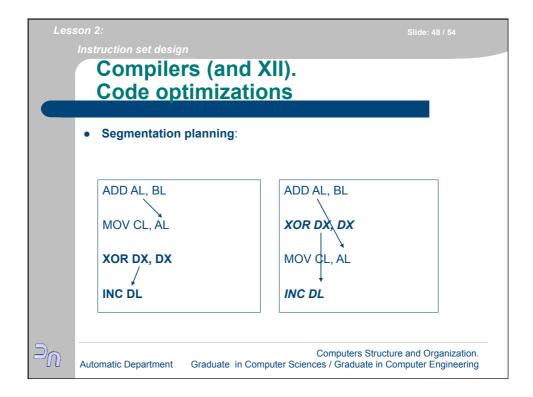

|                         | Segmentation planning                                                                                           | Source code reordering to improve performances and to<br>reduce dependencies between instructions                                     |  |  |

|                         | <ul> <li>Performance can be improved between 60% and 80% by using global<br/>and local optimizations</li> </ul> |                                                                                                                                       |  |  |

| $\supset_{\widehat{N}}$ | Automatic Department Gradu                                                                                      | Computers Structure and Organization.<br>ate in Computer Sciences / Graduate in Computer Engineering                                  |  |  |

| Les                     | son 2: Slide: 50 / 54                                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Instruction set design                                                                                                                                      |

|                         | Instruction sets examples (II). Alpha                                                                                                                       |

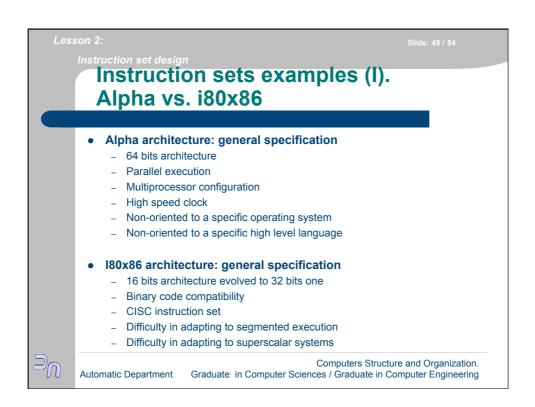

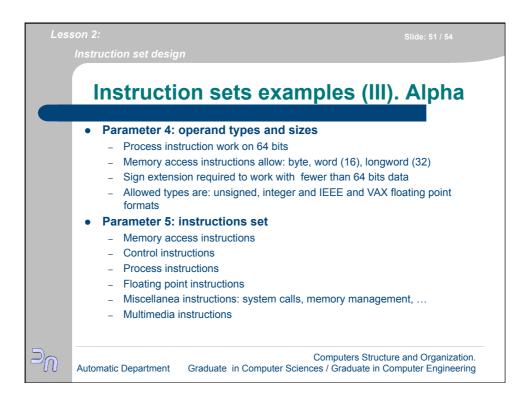

|                         | <ul> <li>Parameter 1: operands storage in cPU</li> <li>32 integer general purpose registers</li> <li>32 floating point general purpose registers</li> </ul> |

|                         | <ul> <li>Parameter 2: explicit operands per instruction</li> <li>3 operands</li> </ul>                                                                      |

|                         | Parameter 3: addressing modes                                                                                                                               |

|                         | <ul><li>Execution model: register-register</li><li>Alignment required</li></ul>                                                                             |

|                         | <ul> <li>Little-endian by default. It's possible to change it to big-endian</li> </ul>                                                                      |

|                         | <ul><li>Unique memory addressing mode: relative to register</li><li>One of the three operands may be an immediate datum</li></ul>                           |

| $\supset_{\widehat{N}}$ | Computers Structure and Organization.<br>Automatic Department Graduate in Computer Sciences / Graduate in Computer Engineering                              |

| Less | n 2: Slide: 52 / 54                                                                                                                                                                                                                                                                                                                                                    |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|      | nstruction set design                                                                                                                                                                                                                                                                                                                                                  |  |

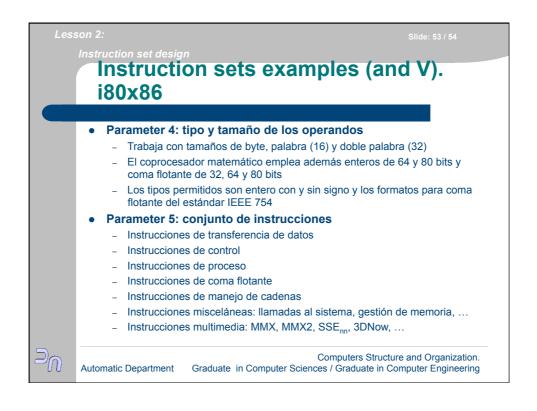

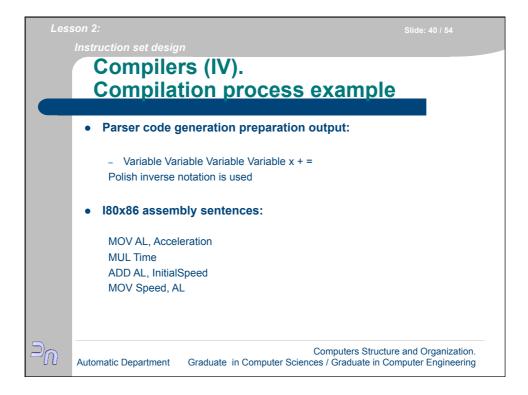

|      | Instruction sets examples (IV). i80x86                                                                                                                                                                                                                                                                                                                                 |  |

|      | <ul> <li>Parameter 1: operands storage in CPU</li> <li>8 integer "quasi" general purpose registers</li> <li>8 floating point "quasi" general purpose registers with stack access</li> </ul>                                                                                                                                                                            |  |

|      | <ul> <li>Parameter 2: explicit operands per instruction</li> <li>2 operands. One of the is source and target of the instruction</li> </ul>                                                                                                                                                                                                                             |  |

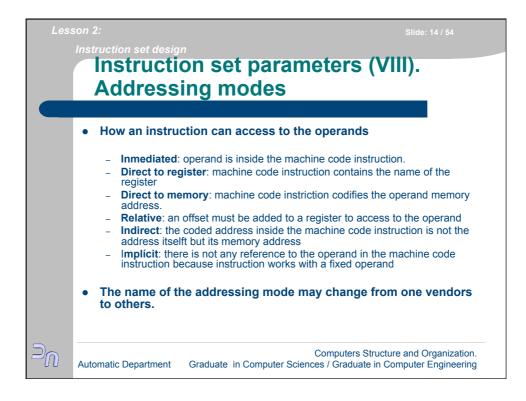

|      | <ul> <li>Parameter 3: adrressing modes         <ul> <li>Execution model: register-memory</li> <li>Alignment recommended but no requested</li> <li>Little-endian</li> <li>Addressing modes: immediate, relative to register, direct to memory, direct to register, indirect and implicit</li> <li>Floating point operand are always in the stack</li> </ul> </li> </ul> |  |

| Ð    | Computers Structure and Organization.<br>Automatic Department Graduate in Computer Sciences / Graduate in Computer Engineering                                                                                                                                                                                                                                         |  |